看到一些新闻,表示某国高科技企业开发了一种新型衬底材料,与GaN晶格匹配,可以良好生长GaN。(备注:GaN体单晶制备难度非常大,因此此处所提的GaN是外延层,此处暴露了外延层存在的意义之一)。那为什么要有衬底及外延层之分呢?外延层的存在有何意义?接下来通过本文一起来探索一下~~

外延Epitaxy这个词来源于希腊字epi,意思是"…之上"

所以常见的GaN on Si的表达也就很容易理解了。

外延片的名字来源

首先,先普及一个小概念:晶圆制备包括衬底制备和外延工艺两大环节。衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。外延(epitaxy)是指在经过切、磨、抛等仔细加工的单晶衬底上生长一层新单晶的过程,新单晶可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延)。由于新生单晶层按衬底晶相延伸生长,从而被称之为外延层(厚度通常为几微米,以硅为例:硅外延生长其意义是在具有一定晶向的硅单晶衬底上生长一层具有和衬底相同晶向的电阻率与厚度不同的晶格结构完整性好的晶体),而长了外延层的衬底称为外延片(外延片=外延层+衬底)。器件制作在外延层上为正外延,若器件制作在衬底上则称为反外延,此时外延层只起支撑作用。

外延工艺解决了什么问题?

只有体单晶材料难以满足日益发展的各种半导体器件制作的需要。因此,1959年末开发了薄层单晶材料生长技外延生长。那外延技术到底对材料的进步有了什么具体的帮助呢?

对于硅而言,硅外延生长技术开始的时候,真是硅高频大功率晶体管制做遇见困难的时刻。从晶体管原理来看,要获得高频大功率,必须做到集电区击穿电压要高,串联电阻要小,即饱和压降要小。前者要求集电区材料电阻率要高,而后者要求集电区材料电阻率要低,两省互相矛盾。如果采用集电极区材料厚度减薄的方式来减少串联电阻,会使硅片太薄易碎,无法加工,若降低材料的电阻率,又与第一个要求矛盾,而外延技术的发展则成功地解决了这一困难。

解决方案:在电阻极低的衬底上生长一层高电阻率外延层,器件制作在外延层上,这样高电阻率的外延层保证了管子有高的击穿电压,而低电阻的衬底又降低了基片的电阻,从而降低了饱和压降,从而解决了二者的矛盾。

此外,GaAs等Ⅲ-Ⅴ族、Ⅱ-Ⅵ族以及其他分子化合物半导体材料的气相外延、液相外延等外延技术也都得到很大的发展,已成为绝大多数书微波器件、光电器件、功率器件等制作不可缺少的工艺技术,特别是分子束、金属有机气相外延技术在薄层、超晶格、量子阱、应变超晶格、原子级薄层外延方面的成功应用,为半导体研究的新领域“能带工程”的开拓打下了夯实的基础。

实际应用中,宽禁带半导体器件几乎都做在外延层上,碳化硅晶片本身只作为衬底,因此外延层的控制可是宽禁带半导体产业重要的一环

PS:引用一下台塑盛高科技官网资料总结一下,epi代表在上方,而taxy则是指规则排列,按字面意义来看,也有它叫磊晶,磊晶晶圆片早期主要用以改善双极电晶体(Bipolartransitors)等元件的品质,近年来也普遍被用在BipolarIC元件及MOS制程上。

外延技术的7大技能

1、可以在低(高)阻衬底上外延生长高(低)阻外延层。

2、可以在P(N)型衬底上外延生长N(P)型外延层,直接形成PN结,不存在用扩散法在单晶基片上制作PN结时的补偿的问题。

3、与掩膜技术结合,在指定的区域进行选择外延生长,为集成电路和结构特殊的器件的制作创造了条件。

4、可以在外延生长过程中根据需要改变掺杂的种类及浓度,浓度的变化可以是陡变的,也可以是缓变的。

5、可以生长异质,多层,多组分化合物且组分可变的超薄层。

6、可在低于材料熔点温度下进行外延生长,生长速率可控,可以实现原子级尺寸厚度的外延生长。

7、可以生长不能拉制单晶材料,如GaN,三、四元系化合物的单晶层等。

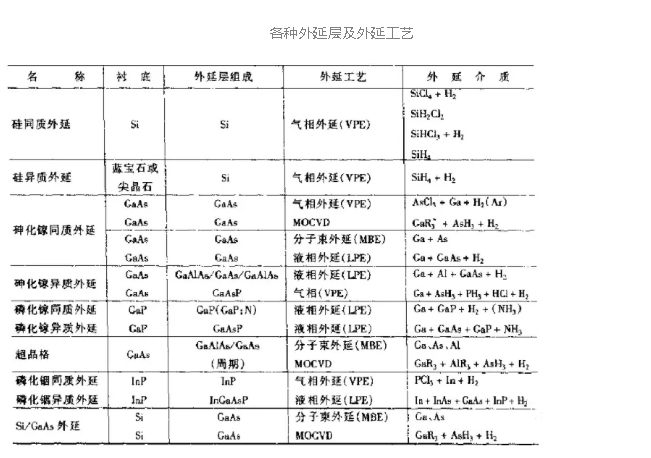

各种外延层及外延工艺

一言以蔽之,外延层比衬底材料更易于获得完美可控的晶体结构,更利于材料的应用开发。